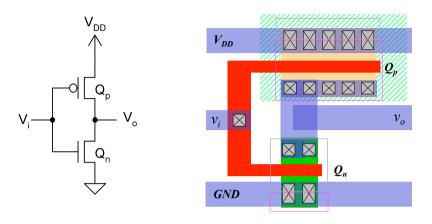

# Layout of a Inverter

# Topic 3

#### **CMOS Fabrication Process**

Peter Cheung

Department of Electrical & Electronic Engineering

Imperial College London

URL: www.ee.ic.ac.uk/pcheung/ E-mail: p.cheung@ic.ac.uk

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 1

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 2

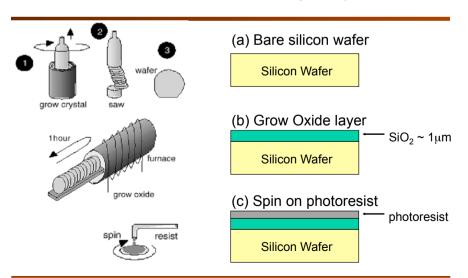

## The CMOS Process - photolithography (1)

# The CMOS Process - photolithography (2)

PYKC Oct-18-10

E4.20 Digital IC Design

Lecture 3 - 3

PYKC Oct-18-10

E4.20 Digital IC Design

Lecture 3 - 4

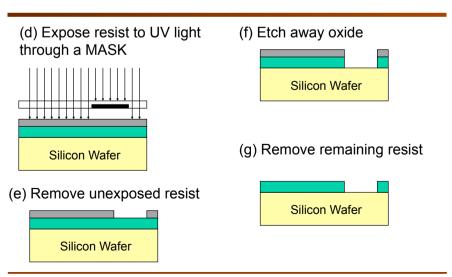

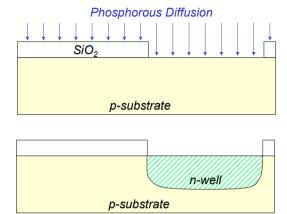

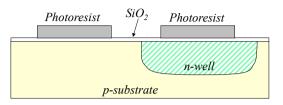

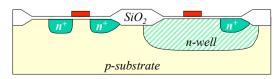

#### Mask 1: N-well Diffusion

Phosphorous is diffused into the unmasked regions of silicon creating an nwell for the fabrication of p-channel devices

## **Mask 3: Polysilicon Gate**

- A high quality thin oxide is grown in the active area (~100Å->300Å)

- Mask 3 is used to deposit the polysilicon gate (most critical step)

The polysilicon layer is usually arsenic doped (n-type). The photolithography in this step is the most demanding since it requires the finest resolution to create the narrow MOS channels.

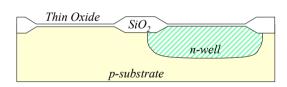

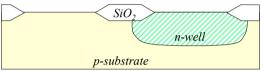

### Mask 2: Define Active Regions

Mask 2 creates the active regions where the MOSFETs will be placed

The thick oxide regions provides isolation between the MOSFETs

A thick field oxide is grown using a contruction technique called Local Oxidation Of Silicon (LOCOS).

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 6

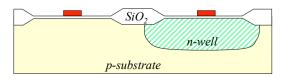

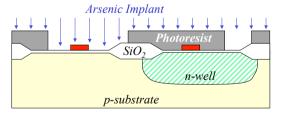

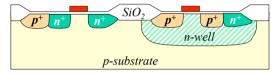

## Mask 4: n+ Diffusion

- Mask 4 is used to control a heavy arsenic implant and create the source and drain of the n-channel devices.

- This is a self-aligned structure.

The polysilicon gate acts like a barrier for this implant to protect the channel region.

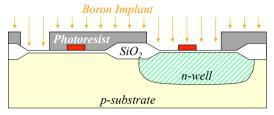

## Mask 5: p+ Diffusion

- Mask 5 is used to control a heavy Boron implant and create the source and drain of the n-channel devices.

- This is a self-aligned structure.

The polysilicon gate acts like a barrier for this implant to protect the channel region.

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 9

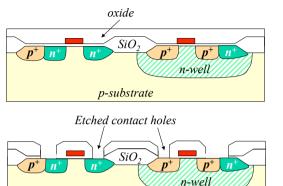

#### Mask 6: Contact Holes

- A thin layer of oxide is deposited over the entire wafer

- Mask 6 is used to pattern the contact holes

- Etching opens the holes.

p-substrate

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 10

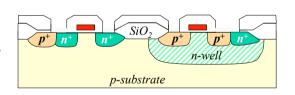

#### Mask 7: Metalization

- A thin layer of aluminum is evaporated or sputtered onto the wafer.

- Mask 7 is used to pattern the interconnection.

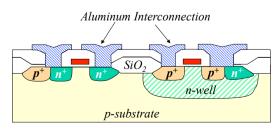

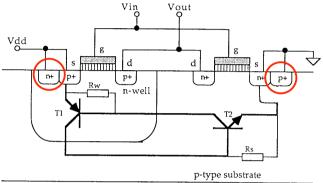

#### **Cross section of a CMOS Inverter**

PYKC Oct-18-10

E4.20 Digital IC Design

Lecture 3 - 11

PYKC Oct-18-10

E4.20 Digital IC Design

Lecture 3 - 12

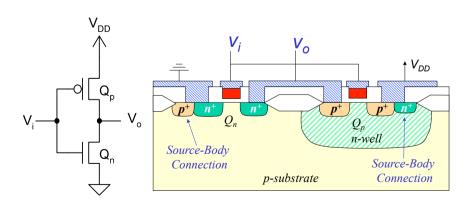

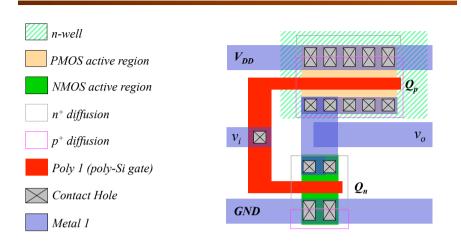

# **Physical Layout of an Inverter**

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 13

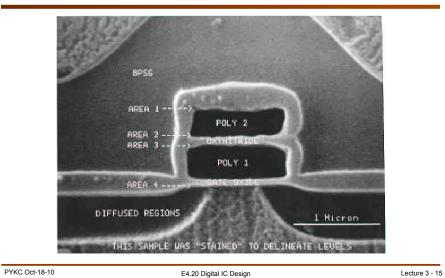

## Photo cross-section of a transistor

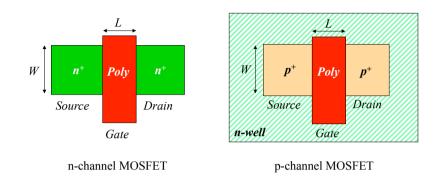

# **Dimension of transistors**

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 14

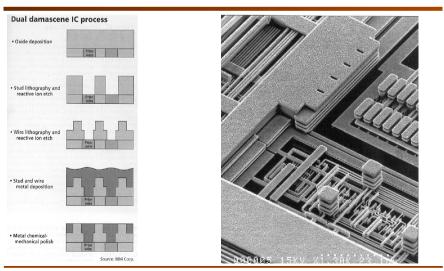

# **Advanced metalization with polishing**

## Latch-up problem (1)

- As shown above, the p+ region of the p-transistor, the n-well and the p- substrate form a

parasitic pnp transistor T1.

- The n- well, the p- substrate and the p+ source of the n-transistor forms another parasitic npn transistor T2.

- There exists two resistors Rw and Rs due to the resistive drop in the well area and the substrate area.

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 17

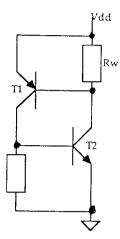

## Latch-up (con't)

- ◆ T1 and T2 form a thyristor circuit.

- If Rw and/or Rs are not 0, and for some reason (power-up, current spike etc), T1 or T2 are forced to conduct, Vdd will be shorted to Gnd through the small resistances and the transistors.

- Once the circuit is 'fired', both transistors will remain conducting due to the voltage drop across Rw and Rs. The only way to get out of this mode is to turn the power off.

- ◆ This condition is known as latch-up.

- To avoid latch-up, substrate-taps (tied to Gnd) and well-taps (tied to Vdd) are inserted as frequently as possible. This has the effect of shorting out Rw and Rs.

PYKC Oct-18-10 E4.20 Digital IC Design Lecture 3 - 18